## **BACHELOR THESIS**

- WORKGROUP TERAHERTZ / PHOTONIK, PROF. DR. V. KROZER -

# Title: Implementation and optimization of a clock distribution in a digital integrated circuit

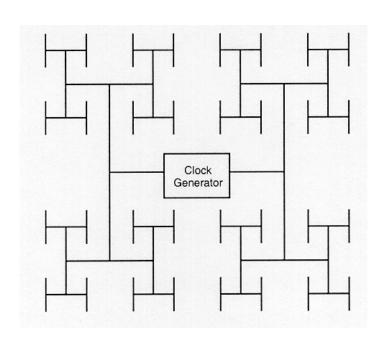

A very important issue in the design of a synchronous digital circuit is the distribution of the clock signal that ensures that all gates on the chip work correctly. For circuits operating at high frequencies this aspect becomes more critical and therefore the clock skew has to be controlled very carefully. In this thesis a clock tree (for instance a H-Tree) shall be implemented/optimized for a *Direct Digital Synthesizer* (DDS).

#### Tasks:

- Comparison of different options of implementing a clok tree

- Implementation and optimization of a clock tree for a DDS

### **Qualifications:**

- familiar with basic electrical engineering

- experienced in working with simulation tools (like ADS, Cadence Virtuoso, SPICE..) would be advantageous

#### Contact details and further information:

André Ehlert

Room: \_0.214, Tel: 069/798-47208 E-mail: ehlert@physik.uni-frankfurt.de

Start: From now on